# A Novel Plus Type DVCC-Based Current-Mode Biquad

Takao Tsukutani<sup>1</sup> and Noboru Yabuki<sup>2</sup>

- 1. National Institute of Technology, Matsue College, Matsue 690-8518, Japan

- 2. National Institute of Technology, Tsuyama College, Tsuyama 708-8509, Japan

**Abstract:** This paper presents a novel current-mode biquad using only plus type DVCCs (differential voltage current conveyors). The circuit enables LP (low-pass), BP (band-pass), HP (high-pass), BS (band-stop) and AP (all-pass) responses by the selection and/or addition of the circuit currents with no component matching constraints. Moreover the circuit parameters  $\omega_0$  and Q can be set orthogonally adjusting the circuit components. An achievement example is given together with simulation results by PSPICE.

**Key words:** Analog circuits, biquad responses, plus type DVCCs.

## 1. Introduction

High performance active circuits have received much attention. The circuit designs using active devices such as CCIIs (second generation current conveyors), the DVCCs (differential voltage current conveyors) and so on have been reported in Refs. [1-4].

A DVCC is a very useful active device, and DVCC-based circuit is adaptable to wide band operation. A plus type DVCC is composed of simpler circuit configuration than a minus type one. Hence it has wide band operation and low power performance compared with the minus type DVCC.

Till now several biquads employing the DVCCs have been discussed [2-4]. However, plus type DVCC-based biquad [4] has not yet been studied sufficiently.

This paper introduces a novel current-mode biquad. First we show a basic current-mode biquad using only the plus type DVCCs and grounded passive components. Then typical current-mode biquad is consisted of using the basic current-mode one. The circuit enables LP (low-pass), BP (band-pass), HP (high-pass), BS (band-stop) and AP (all-pass) responses by the selection and/or addition of the input

and output currents with no component matching constraints. And the circuit parameters  $\omega_0$  and Q can be set orthogonally by the circuit components.

The achievement example is given with PSPICE simulations, and the circuit workability is confirmed.

## 2. DVCC and Its Performance

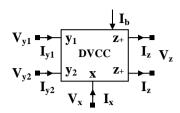

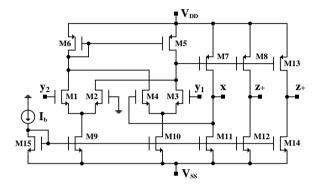

The symbol of the plus type DVCC is given in Fig. 1, and Fig. 2 shows the DVCC with MOS transistors. The plus type DVCC is characterized by the following terminal equation:

$$V_x = V_{v1} - V_{v2}, \quad I_z = I_x$$

(1)

# 3. DVCC-Based Biquad

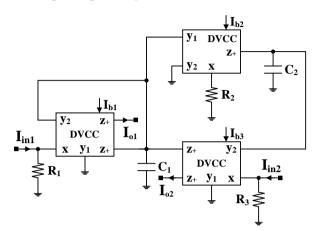

Fig. 3 shows the basic current-mode biquad configuration. The current outputs  $I_{o1}(s)$  and  $I_{o2}(s)$  are given by:

$$I_{o1}(s) = -\frac{(s^2 + 1/C_1C_2R_2R_3)I_{in1}(s) - (1/C_1R_1)sI_{in2}(s)}{s^2 + (1/C_1R_1)s + 1/C_1C_2R_2R_3}$$

(2)

$$I_{o2}(s) = -\frac{-(1/C_1C_2R_2R_3)I_{in1}(s) + (s^2 + (1/C_1R_1)s)I_{in2}(s)}{s^2 + (1/C_1R_1)s + 1/C_1C_2R_2R_3}$$

(3)

This circuit enables the LP, BP and BS responses by selection of the input and output currents as follows:

$$T_{LP}(s) = \frac{I_{o2}(s)}{I_{in1}(s)} = \frac{1/C_1C_2R_2R_3}{s^2 + (1/C_1R_1)s + 1/C_1C_2R_2R_3}$$

(4)

$$T_{BP}(s) = \frac{I_{o1}(s)}{I_{in2}(s)} = \frac{(1/C_1R_1)s}{s^2 + (1/C_1R_1)s + 1/C_1C_2R_2R_3}$$

(5)

**Corresponding author:** Takao Tsukutani, PhD, research field: analog signal processing.

Fig. 1 Symbol for DVCC.

Fig. 2 DVCC with MOS transistors.

$$T_{BS}(s) = \frac{I_{o1}(s)}{I_{in1}(s)} = -\frac{s^2 + 1/C_1C_2R_2R_3}{s^2 + (1/C_1R_1)s + 1/C_1C_2R_2R_3}$$

(6)

Moreover the HP response can be achieved by the current addition of  $I_{\rm HP}(s) = I_{\rm o1}(s) + I_{\rm o2}(s)$ , and the AP response is performed selecting the input current  $I_{\rm in}(s) = I_{\rm in1}(s) = I_{\rm in2}(s)$ . The circuit transfer functions are given as:

$$T_{HP}(s) = \frac{I_{HP}(s)}{I_{in1}(s)} = -\frac{s^2}{s^2 + (1/C_1R_1)s + 1/C_1C_2R_2R_3}$$

(7)

$$T_{AP}(s) = \frac{I_{o1}(s)}{I_{in}(s)} = -\frac{s^2 - (1/C_1R_1)s + 1/C_1C_2R_2R_3}{s^2 + (1/C_1R_1)s + 1/C_1C_2R_2R_3}$$

(8)

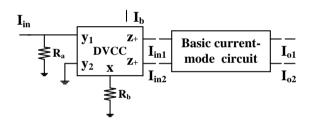

The typical current-mode biquad is consisted of using the basic current-mode one shown in Fig. 4.

The circuit parameters  $\omega_0$ , Q and H are represented as below:

$$\omega_{0} = \sqrt{\frac{1}{C_{1}C_{2}R_{2}R_{3}}}, \quad Q = R_{1}\sqrt{\frac{C_{1}}{C_{2}R_{2}R_{3}}}, \quad H = \frac{R_{a}}{R_{b}} \quad (9)$$

The circuit parameters  $\omega_0$  and Q can be set orthogonally, and meanwhile the parameter H is able to set independently.

## 4. A Design Example and Simulation Results

As a design example, we tried to achieve a current-mode biquad with  $f_0$  (=  $\omega_0/2\pi$ ) = 1 MHz, Q =

1.0 and H=1.0. To realize the specification above, we set that the circuit resistors and capacitors were  $R_1=R_2=R_3=12.3 \text{ k}\Omega$ ,  $R_a=12 \text{ k}\Omega$ ,  $R_b=10 \text{ k}\Omega$  and  $C_1=C_2=12 \text{ pF}$ , respectively.

Fig. 3 Basic current-mode biquad.

Fig. 4 Typical current-mode biquad.

Fig. 5 Simulation responses.

Fig. 5 shows the simulation responses ((a) LP, BP, HP, BS responses, (b) AP response) with PSPICE. In the figures, the marks signify the simulation responses, and the continuous lines show the theoretical ones. This can be viewed as an excellent result. Here we set that the input current, bias currents and DC supply voltages of the DVCCs were  $I_{\rm in}=10~\mu{\rm A},~I_{\rm b1}=I_{\rm b2}=I_{\rm b3}=I_{\rm b}=10~\mu{\rm A}$  and  $V_{\rm DD}=-V_{\rm SS}=0.8~{\rm V}$ , respectively. The power dissipation was 0.351 mW. In this simulation, the MOS transistor aspect ratios were set as 20  $\mu{\rm m}/0.5~\mu{\rm m}$  (M1 to M4), 30  $\mu{\rm m}/2~\mu{\rm m}$  (M5 to M8, M13) and 10  $\mu{\rm m}/2~\mu{\rm m}$  (M9 to M12, M14, M15). Also we used the device parameters from MOSIS 0.5  $\mu{\rm m}$ .

## 5. Conclusions

This paper has described a novel current-mode biquad employing plus type DVCCs and grounded passive components. The circuit can achieve the standard circuit responses by selecting and/or adding the circuit currents.

The achievement example has been given together with simulation results. The simulation responses were appropriate enough over a wide frequency range. The circuit configuration is very suitable for implementation in CMOS technology.

## References

- [1] Fabre, A., et al. 1996. "High Frequency Applications Based on a New Current Controlled Conveyor." *IEEE Transactions on Circuits and Systems* 43 (2): 82-91.

- [2] Elwan, H. O., and Soliman, A. M. 1997. "Novel CMOS Differential Voltage Current Conveyor and Its Applications." *IEEE Proceedings on Circuits, Devices* and Systems 144 (3): 195-200.

- [3] Ibrahim, M. A., et al. 2005. "A 22.5 MHz Current-Mode KHN-Biquad Using Differential Voltage Current Conveyor and Grounded Passive Elements." *International Journal of Electronics and Communications* 59: 311-8.

- [4] Tsukutani, T., et al. 2007. "Novel Current-Mode Biquadratic Circuit Using Only Plus Type DO-DVCCs and Grounded Passive Components." *International Journal of Electronics* 94 (12): 1137-46.